今天開始的幾天要來跟大家分享語法,那今天要講的是比較偏向於判斷式的使用,首先先來介紹:

if… else…

,使用方式跟C語言很像,舉個例子:

always@(posedge clk)begin

if(reset)begin

end

else if(判斷條件 1)begin

敘述1

end

else if(判斷條件 2)begin

敘述2

end

.

.

.

.

.

.

else begin

敘述n

end

end

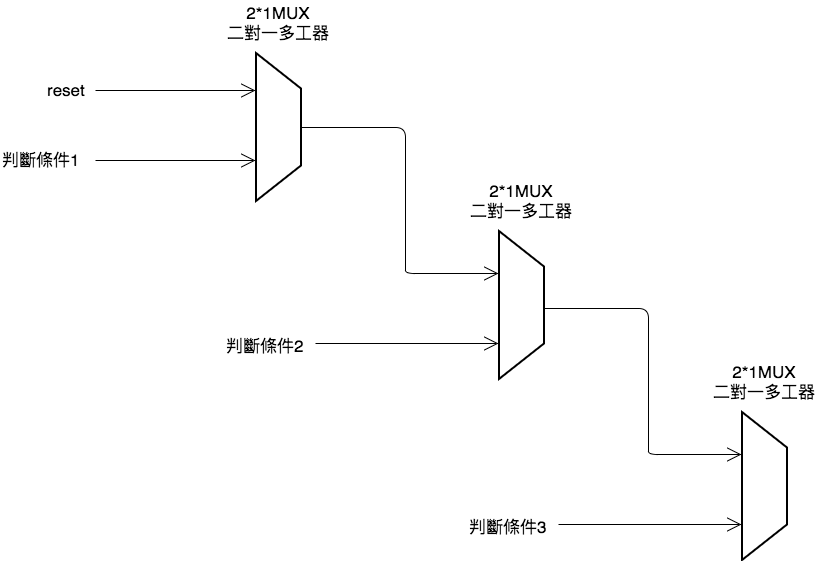

if else的特性就是使用時會根據判斷式的先後順序有優先權的不同,以上面的例子就是reset >判斷條件1>判斷條件2>....>判斷條件n,利用圖解的方式讓大家知道這種判斷式會合成出怎麼樣的電路,

如上圖所示,如果寫if else判斷式的話,合成出來的電路大概長這樣,會產生有優先權關係的數個二對一的多工器去產生你要的電路,也因為這樣,所以當判斷式越多的時候,所造成的路徑也會越長,這樣可能造成合成出來的電路因為路徑在長造成timing可能就會violation,這便大約提一下,timing,假設說妳的clock rate是100MHz,代表一個cycle是10ns,意味著暫存器跟暫存器之間的邏輯運算要在10ns內完成動作,不然就會因為時間內做不完邏輯運算而導致合成錯誤.

再來要介紹的是:

case

來看一下例子:

always@(posedge clk)begin

if(reset)begin

counter <= 0;

end

else begin

case(狀態選擇)

選擇一:

敘述一

選擇二:

敘述二

選擇三:

敘述三

.

.

.

.

選擇n:

敘述n

default:

敘述x

endcase

end

end

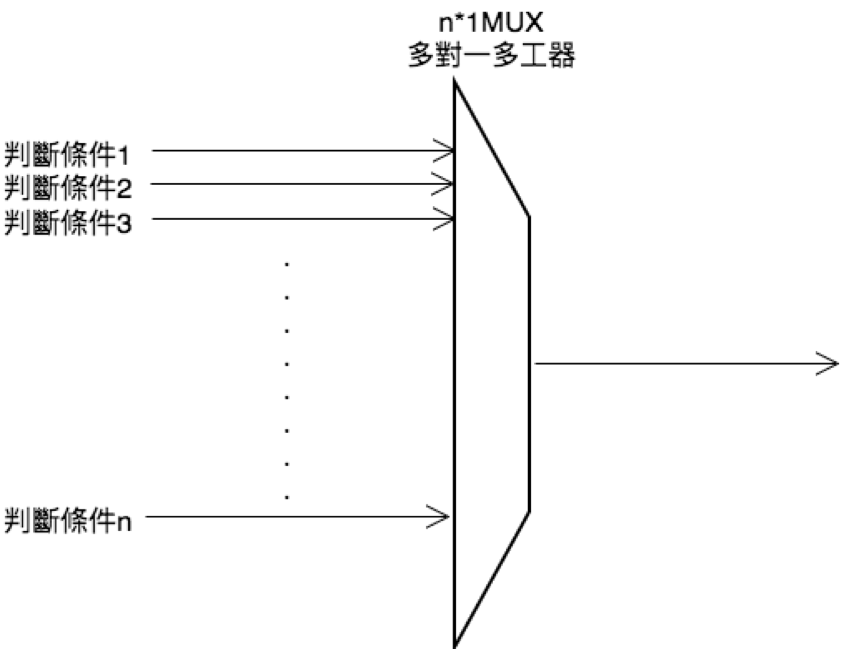

用case去寫判斷式時就會產生多對一的多工器,如下圖.

如果當你的選擇條件是有辦法用case去寫的話,通常就會用case去寫,讓path越短越好,path,timing最後幾個章節如果有空的話會再多介紹.

今天這樣搭配電路圖來了解verilog的語法是不是比較易懂呢,今天就先介紹到這裡,往後的教學大多也會畫圖來跟大家分享喔.